UNIVERSITY OF CALIFORNIA, SAN DIEGO

**Succinct and Assured Machine Learning: Training and Execution**

A dissertation submitted in partial satisfaction of the

requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Computer Engineering)

by

Bita Darvish Rouhani

Committee in charge:

Professor Farinaz Koushanfar, Chair

Professor Hadi Esmaeilzadeh

Professor Tara Javidi

Professor Truong Nguyen

Professor Bhaskar Rao

Professor Tajana Simunic Rosing

2018

Copyright

Bita Darvish Rouhani, 2018

All rights reserved.

The dissertation of Bita Darvish Rouhani is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

## Chair

University of California, San Diego

2018

## DEDICATION

To my beloved parents Mahin and Behrouz.

## TABLE OF CONTENTS

|                                                                                                    |      |

|----------------------------------------------------------------------------------------------------|------|

| Signature Page . . . . .                                                                           | iii  |

| Dedication . . . . .                                                                               | iv   |

| Table of Contents . . . . .                                                                        | v    |

| List of Figures . . . . .                                                                          | ix   |

| List of Tables . . . . .                                                                           | xii  |

| Acknowledgements . . . . .                                                                         | xiv  |

| Vita . . . . .                                                                                     | xvii |

| Abstract of the Dissertation . . . . .                                                             | xx   |

| <br>                                                                                               |      |

| Chapter 1      Introduction . . . . .                                                              | 1    |

| 1.1     Resource-Efficient and Trusted Deep Learning . . . . .                                     | 2    |

| 1.1.1    Succinct Training and Execution of Deep Neural Networks . . . . .                         | 3    |

| 1.1.2    Assured Deep Neural Networks Against Adversarial Attacks . . . . .                        | 5    |

| 1.1.3    Watermarking of Deep Neural Networks . . . . .                                            | 7    |

| 1.1.4    Privacy-Preserving Deep Learning . . . . .                                                | 9    |

| 1.2     Real-Time Causal Bayesian Analysis . . . . .                                               | 11   |

| 1.3     Broader Impact and Re-usability . . . . .                                                  | 12   |

| <br>                                                                                               |      |

| Chapter 2      Background . . . . .                                                                | 13   |

| 2.1     Machine Learning . . . . .                                                                 | 13   |

| 2.1.1    Deep Learning . . . . .                                                                   | 14   |

| 2.1.2    Causal Bayesian Graphical Analysis . . . . .                                              | 16   |

| 2.2     Secure Function Evaluation . . . . .                                                       | 18   |

| 2.2.1    Oblivious Transfer . . . . .                                                              | 18   |

| 2.2.2    Garbled Circuit . . . . .                                                                 | 19   |

| 2.2.3    Garbled Circuit Optimizations . . . . .                                                   | 20   |

| 2.3     Acknowledgements . . . . .                                                                 | 22   |

| <br>                                                                                               |      |

| Chapter 3      Deep3: Leveraging Three Levels of Parallelism for Efficient Deep Learning . . . . . | 23   |

| 3.1     Introduction . . . . .                                                                     | 23   |

| 3.2     Deep3 Global Flow . . . . .                                                                | 26   |

| 3.3     Hardware Parallelism . . . . .                                                             | 28   |

| 3.4     Neural Network Parallelism . . . . .                                                       | 28   |

| 3.4.1    Parameter Coordination . . . . .                                                          | 30   |

| 3.4.2    Computation-Communication Trade-off . . . . .                                             | 32   |

|                  |                                                                                |           |

|------------------|--------------------------------------------------------------------------------|-----------|

| 3.5              | Data Parallelism . . . . .                                                     | 33        |

| 3.6              | Experiments . . . . .                                                          | 35        |

| 3.6.1            | Deep3 Performance Evaluation . . . . .                                         | 36        |

| 3.7              | Summary . . . . .                                                              | 39        |

| 3.8              | Acknowledgements . . . . .                                                     | 39        |

| <b>Chapter 4</b> | <b>DeepFense: Online Accelerated Defense Against Adversarial Deep Learning</b> | <b>40</b> |

| 4.1              | Introduction . . . . .                                                         | 41        |

| 4.2              | DeepFense Global Flow . . . . .                                                | 44        |

| 4.3              | DeepFense Methodology . . . . .                                                | 46        |

| 4.3.1            | Motivational Example . . . . .                                                 | 46        |

| 4.3.2            | Latent Defenders . . . . .                                                     | 47        |

| 4.3.3            | Input Defender . . . . .                                                       | 50        |

| 4.3.4            | Model Fusion . . . . .                                                         | 51        |

| 4.4              | DeepFense Hardware Acceleration . . . . .                                      | 52        |

| 4.4.1            | Latent Defenders . . . . .                                                     | 53        |

| 4.4.2            | Input Defenders . . . . .                                                      | 55        |

| 4.4.3            | Automated Design Customization . . . . .                                       | 57        |

| 4.5              | Experiments . . . . .                                                          | 59        |

| 4.5.1            | Attack Analysis and Resiliency . . . . .                                       | 59        |

| 4.5.2            | Performance Analysis . . . . .                                                 | 61        |

| 4.5.3            | Transferability of Adversarial Samples . . . . .                               | 63        |

| 4.6              | Related Work . . . . .                                                         | 64        |

| 4.7              | Summary . . . . .                                                              | 65        |

| 4.8              | Acknowledgements . . . . .                                                     | 65        |

| <b>Chapter 5</b> | <b>DeepSigns: Watermarking Deep Neural Networks</b>                            | <b>67</b> |

| 5.1              | Introduction . . . . .                                                         | 68        |

| 5.2              | DeepSigns Global Flow . . . . .                                                | 71        |

| 5.2.1            | DNN Watermarking Prerequisites . . . . .                                       | 73        |

| 5.3              | DeepSigns Methodology . . . . .                                                | 74        |

| 5.3.1            | Watermarking Intermediate Layers . . . . .                                     | 75        |

| 5.3.2            | Watermarking Output Layer . . . . .                                            | 79        |

| 5.3.3            | DeepSigns Watermark Extraction Overhead . . . . .                              | 86        |

| 5.4              | Evaluations . . . . .                                                          | 86        |

| 5.4.1            | Fidelity . . . . .                                                             | 87        |

| 5.4.2            | Reliability and Robustness . . . . .                                           | 88        |

| 5.4.3            | Integrity . . . . .                                                            | 90        |

| 5.4.4            | Capacity . . . . .                                                             | 91        |

| 5.4.5            | Efficiency . . . . .                                                           | 92        |

| 5.4.6            | Security . . . . .                                                             | 93        |

| 5.5              | Comparison With Prior Works . . . . .                                          | 94        |

| 5.5.1            | Intermediate Layer Watermarking . . . . .                                      | 94        |

|           |                                                                                     |     |

|-----------|-------------------------------------------------------------------------------------|-----|

| 5.5.2     | Output Layer Watermarking . . . . .                                                 | 95  |

| 5.6       | Summary . . . . .                                                                   | 96  |

| 5.7       | Acknowledgements . . . . .                                                          | 96  |

| Chapter 6 | DeepSecure: Scalable Provably-Secure Deep Learning . . . . .                        | 97  |

| 6.1       | Introduction . . . . .                                                              | 98  |

| 6.2       | DeepSecure Framework . . . . .                                                      | 100 |

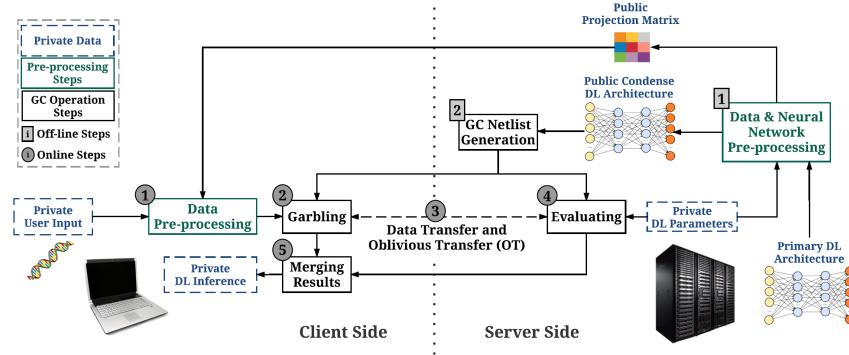

| 6.2.1     | DeepSecure GC Core Structure . . . . .                                              | 100 |

| 6.2.2     | Data and DL Network Pre-processing . . . . .                                        | 102 |

| 6.2.3     | GC-Optimized Circuit Components Library . . . . .                                   | 105 |

| 6.2.4     | Security Proof . . . . .                                                            | 106 |

| 6.3       | Evaluations . . . . .                                                               | 108 |

| 6.4       | Related Work . . . . .                                                              | 110 |

| 6.5       | Summary . . . . .                                                                   | 112 |

| 6.6       | Acknowledgements . . . . .                                                          | 112 |

| Chapter 7 | ReDCrypt: Real-Time Privacy-Preserving Deep Learning Inference in Clouds            | 113 |

| 7.1       | Introduction . . . . .                                                              | 114 |

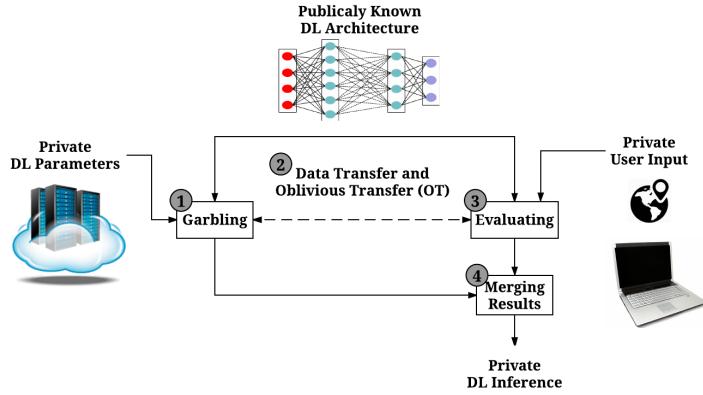

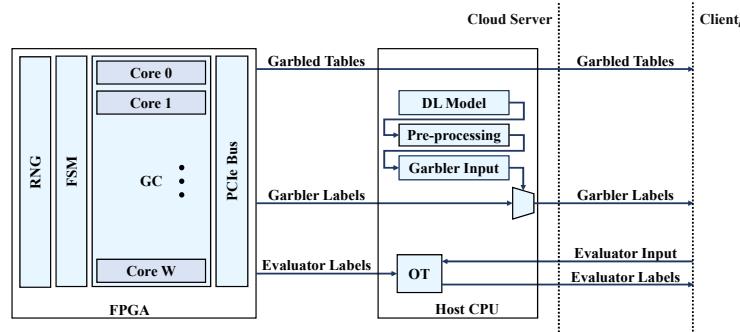

| 7.2       | ReDCrypt Global Flow . . . . .                                                      | 117 |

| 7.2.1     | Security Model . . . . .                                                            | 119 |

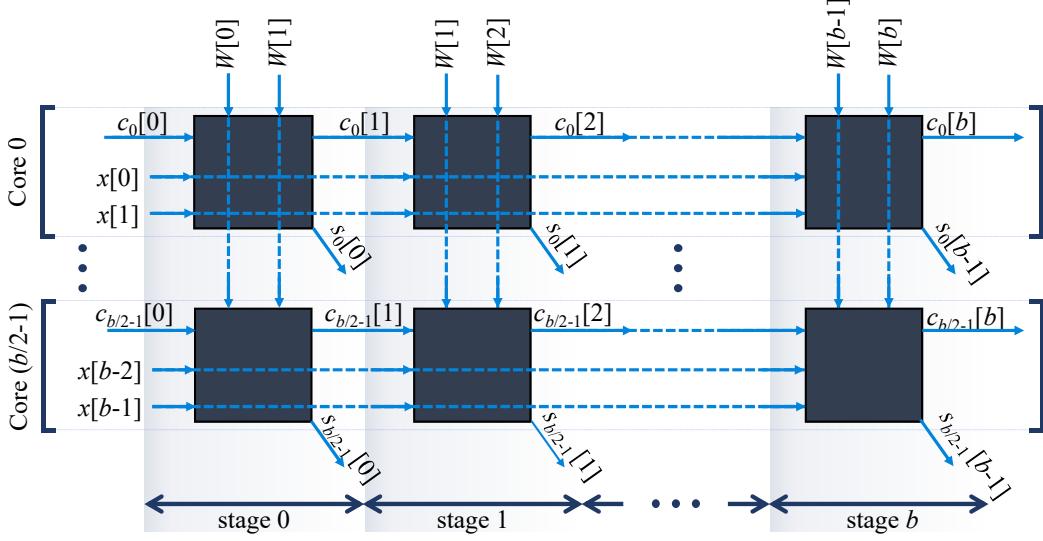

| 7.3       | System Architecture . . . . .                                                       | 120 |

| 7.3.1     | Host CPU . . . . .                                                                  | 123 |

| 7.3.2     | FPGA Accelerator . . . . .                                                          | 123 |

| 7.4       | Configuration of the GC Cores . . . . .                                             | 124 |

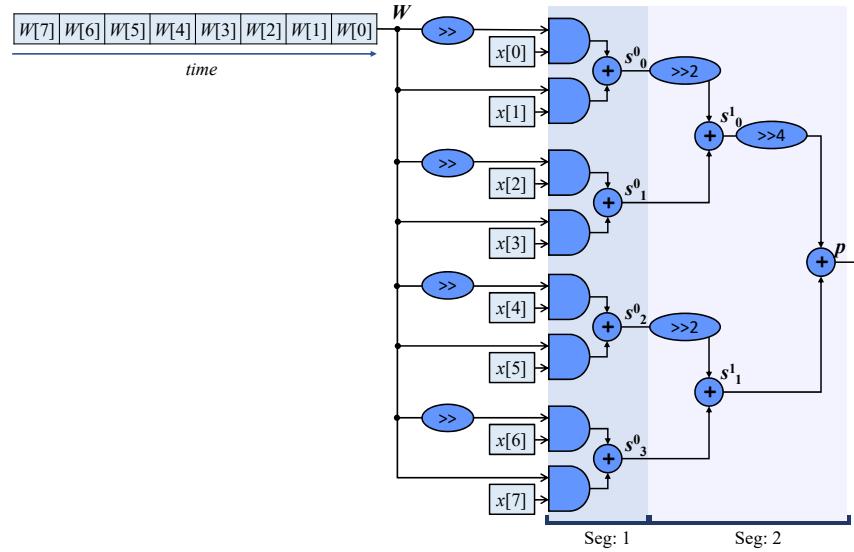

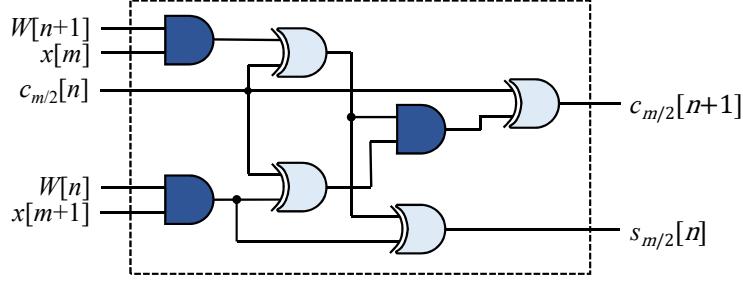

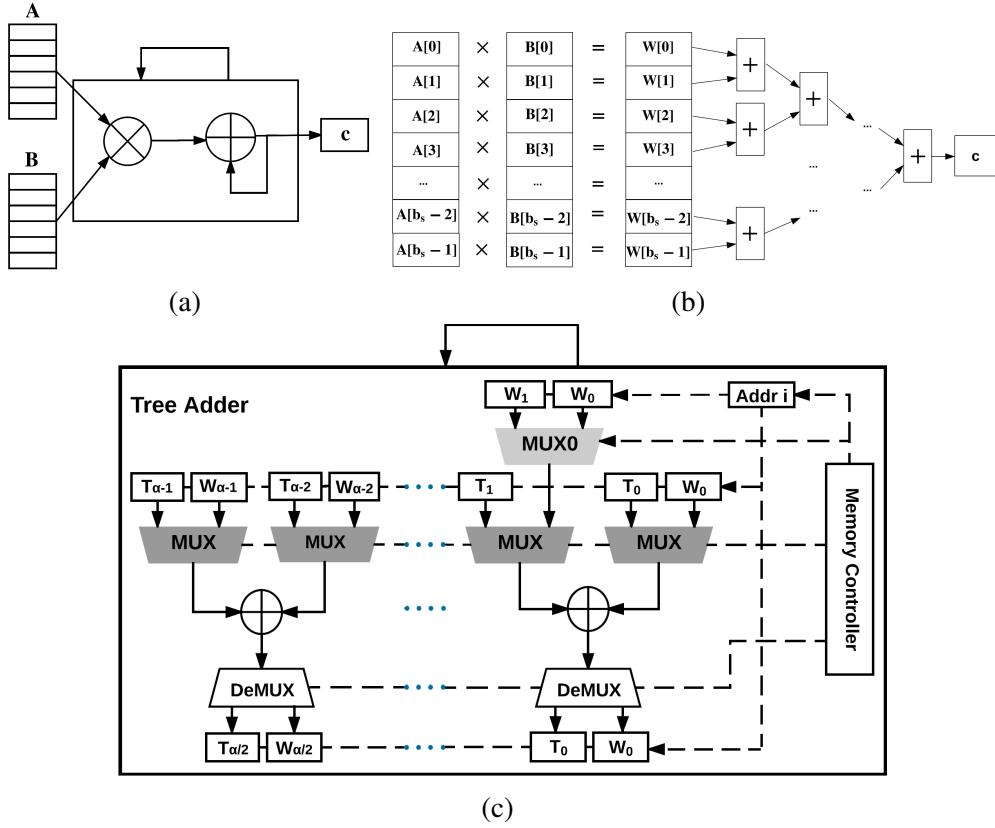

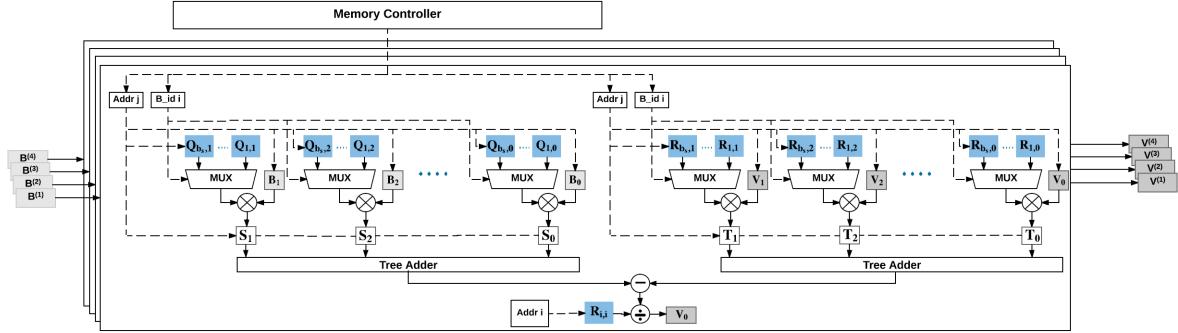

| 7.4.1     | Segment 1: MUX_ADD . . . . .                                                        | 126 |

| 7.4.2     | Segment 2: TREE . . . . .                                                           | 127 |

| 7.4.3     | Accumulator, Support for Signed Inputs and Relu . . . . .                           | 128 |

| 7.4.4     | Scalability Analysis . . . . .                                                      | 128 |

| 7.5       | Hardware Setting and Results . . . . .                                              | 129 |

| 7.5.1     | GC Engine . . . . .                                                                 | 129 |

| 7.5.2     | Label Generator . . . . .                                                           | 130 |

| 7.5.3     | Resource Utilization . . . . .                                                      | 131 |

| 7.5.4     | Performance Comparison with the Prior-art GC Implementation                         | 132 |

| 7.6       | Practical Design Experiments . . . . .                                              | 133 |

| 7.6.1     | Deep Learning Benchmarks . . . . .                                                  | 133 |

| 7.6.2     | Generic ML Applications . . . . .                                                   | 134 |

| 7.7       | Related Work . . . . .                                                              | 136 |

| 7.8       | Summary . . . . .                                                                   | 137 |

| 7.9       | Acknowledgements . . . . .                                                          | 138 |

| Chapter 8 | CausaLearn: Scalable Streaming-based Causal Bayesian Learning using FPGAs . . . . . | 139 |

| 8.1       | Introduction . . . . .                                                              | 140 |

|              |                                        |     |

|--------------|----------------------------------------|-----|

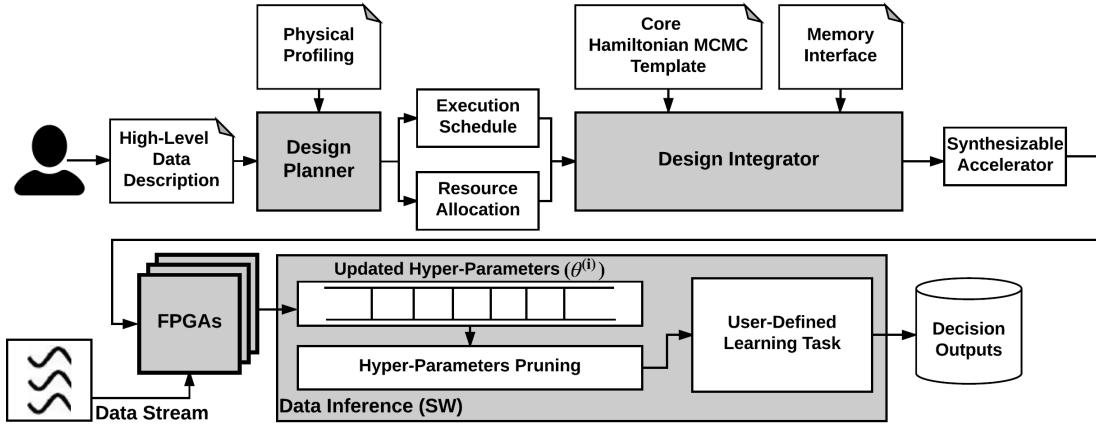

| 8.2          | CausaLearn Global Flow . . . . .       | 144 |

| 8.3          | CausaLearn Framework . . . . .         | 146 |

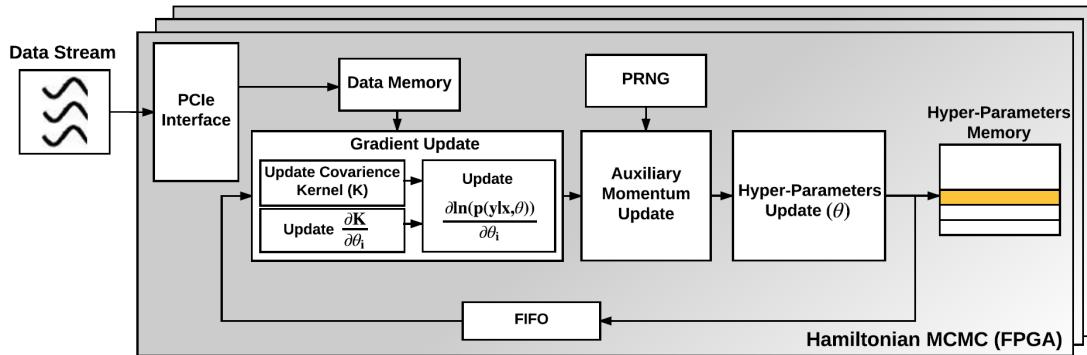

| 8.4          | Accelerator Architecture . . . . .     | 149 |

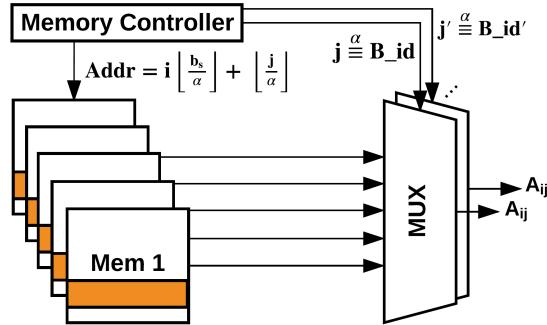

| 8.4.1        | Hardware Implementation . . . . .      | 151 |

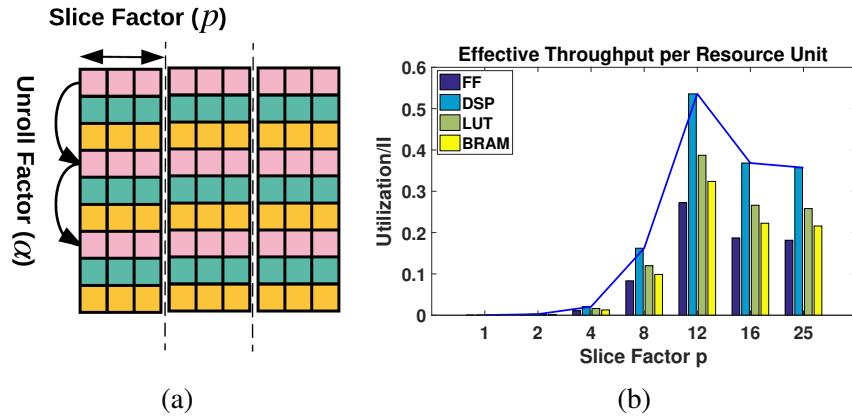

| 8.5          | CausaLearn Customization . . . . .     | 157 |

| 8.5.1        | Design Planner . . . . .               | 157 |

| 8.5.2        | Design Integrator . . . . .            | 160 |

| 8.5.3        | CausaLearn API . . . . .               | 160 |

| 8.6          | Hardware Setting and Results . . . . . | 161 |

| 8.7          | Practical Design Experiences . . . . . | 163 |

| 8.8          | Related Work . . . . .                 | 165 |

| 8.9          | Summary . . . . .                      | 166 |

| 8.10         | Acknowledgements . . . . .             | 167 |

| Chapter 9    | Summary and Future Work . . . . .      | 168 |

| Bibliography | . . . . .                              | 170 |

## LIST OF FIGURES

|                                                                                                                                                                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1: Research overview. My work enables the next generation of cyber-physical applications by devising holistic computing frameworks that are simultaneously optimized for the underlying data, learning algorithm, hardware, and security requirements. . . . .                                | 2  |

| Figure 1.2: Comparison of several state-of-the-art deep learning frameworks in terms of their high-level characteristics and features. . . . .                                                                                                                                                         | 4  |

| Figure 1.3: The left image is a legitimate “stop” sign sample that is classified correctly by an ML model. The right image, however, is an adversarial input crafted by adding a particular perturbation that makes the same model classify it as a “yield” sign. . . . .                              | 6  |

| Figure 1.4: High-level comparison between state-of-the-art watermarking frameworks for deep neural networks. . . . .                                                                                                                                                                                   | 9  |

| Figure 1.5: High-level characteristics of existing frameworks for privacy-preserving execution of deep learning models and their corresponding cryptographic primitives. . . . .                                                                                                                       | 10 |

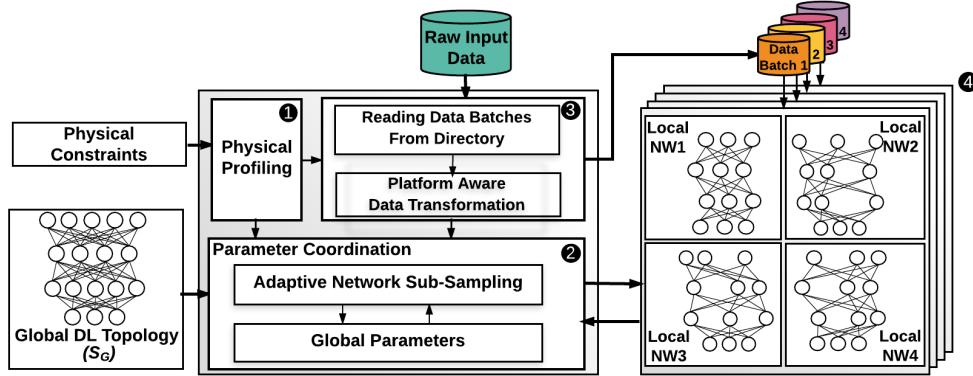

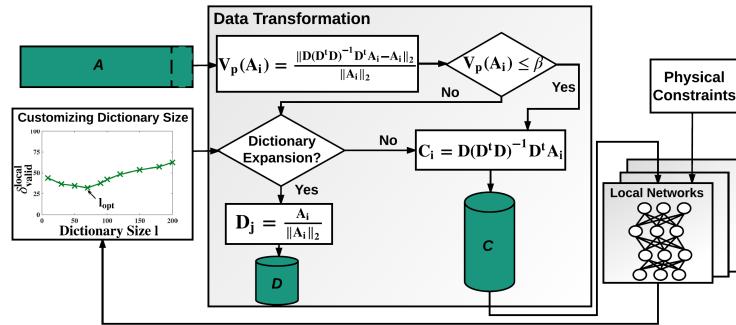

| Figure 3.1: Global flow of Deep3 framework. . . . .                                                                                                                                                                                                                                                    | 27 |

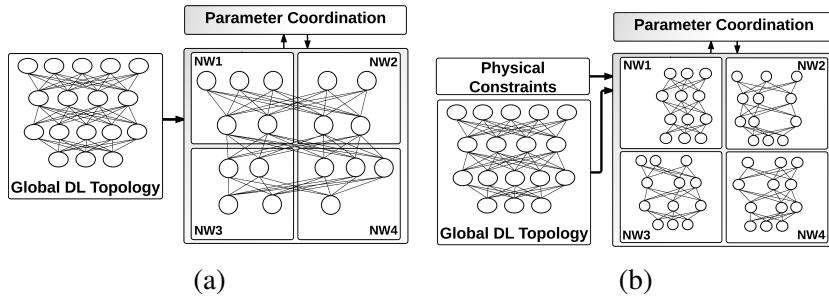

| Figure 3.2: Network parallelism in Deep3 framework. . . . .                                                                                                                                                                                                                                            | 29 |

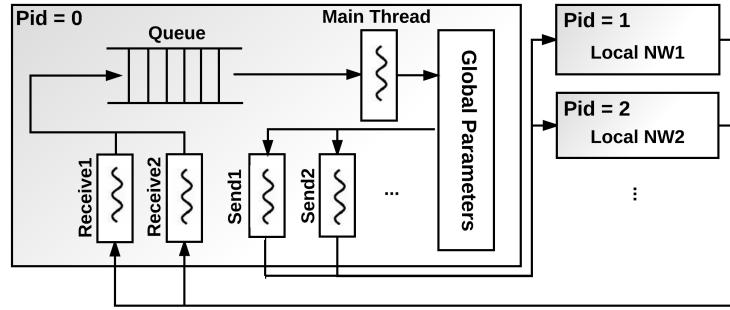

| Figure 3.3: Flow of data in Deep3 framework. . . . .                                                                                                                                                                                                                                                   | 30 |

| Figure 3.4: Data Parallelism in Deep3 framework. . . . .                                                                                                                                                                                                                                               | 34 |

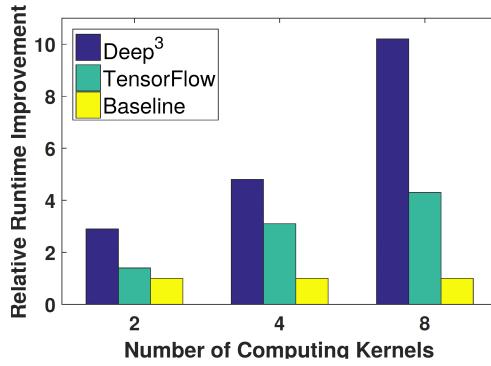

| Figure 3.5: Deep3 relative runtime improvement. . . . .                                                                                                                                                                                                                                                | 38 |

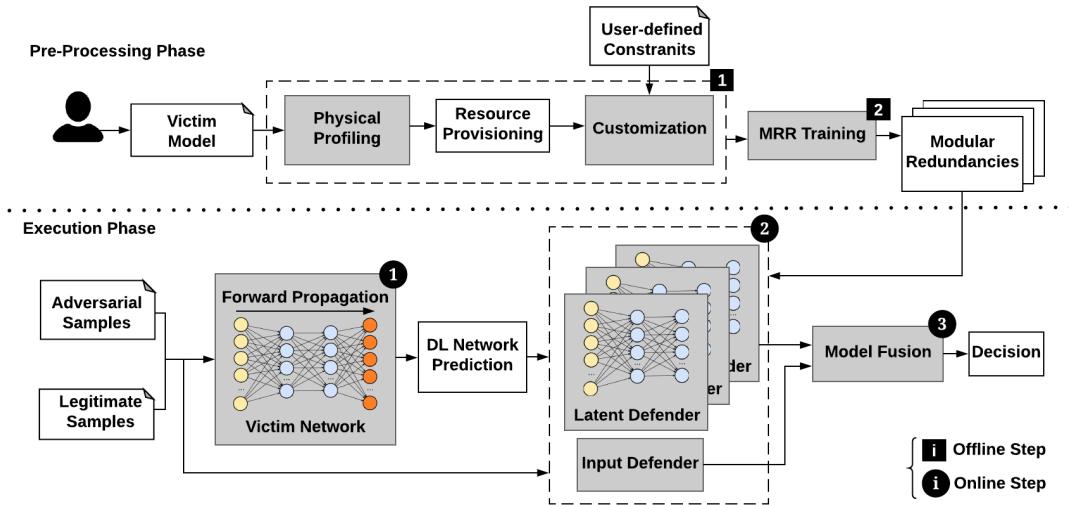

| Figure 4.1: Global flow of the DeepFense framework. . . . .                                                                                                                                                                                                                                            | 44 |

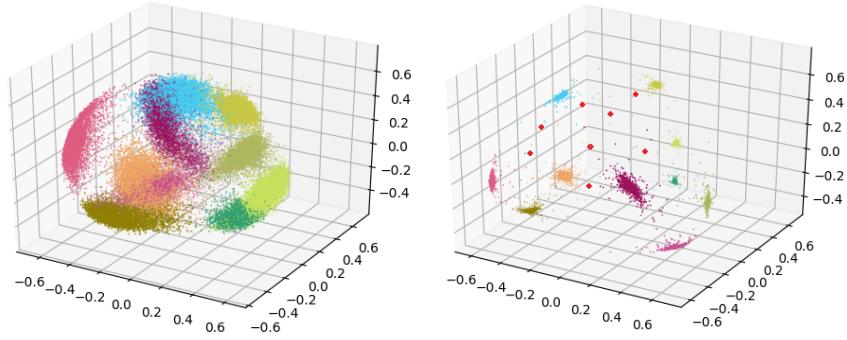

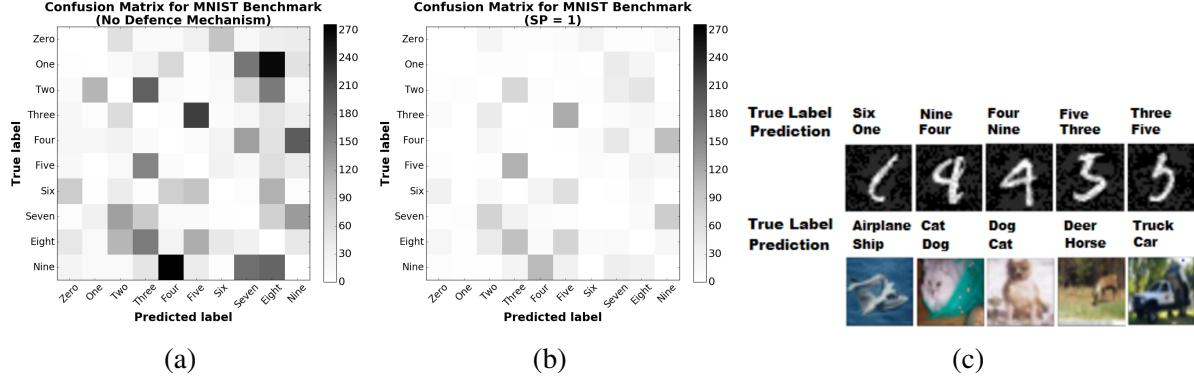

| Figure 4.2: Example feature samples in the second-to-last layer of LeNet3 model trained for classifying MNIST data before (left figure) and after (right figure) data realignment performed in Step 2. The majority of adversarial samples (the red dot points) reside in low density regions. . . . . | 49 |

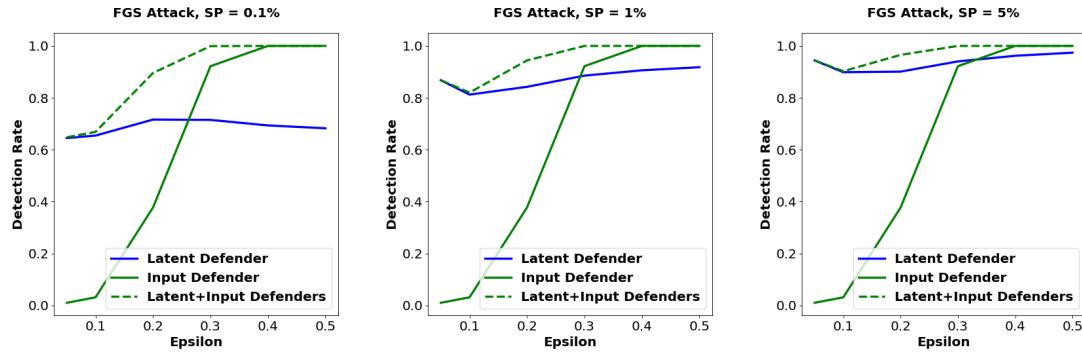

| Figure 4.3: Adversarial detection rate of the latent and input defender modules as a function of the perturbation level. . . . .                                                                                                                                                                       | 51 |

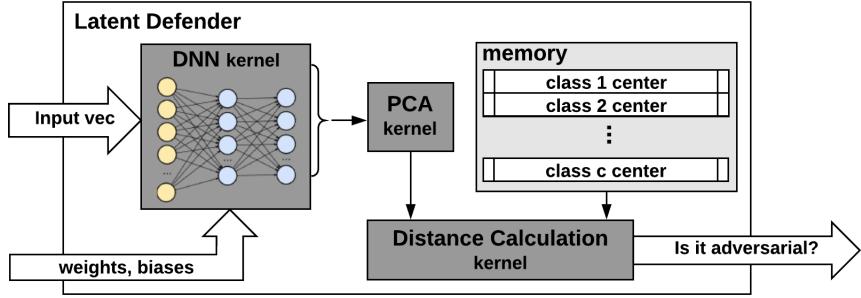

| Figure 4.4: Architecture of DeepFense latent defender. . . . .                                                                                                                                                                                                                                         | 54 |

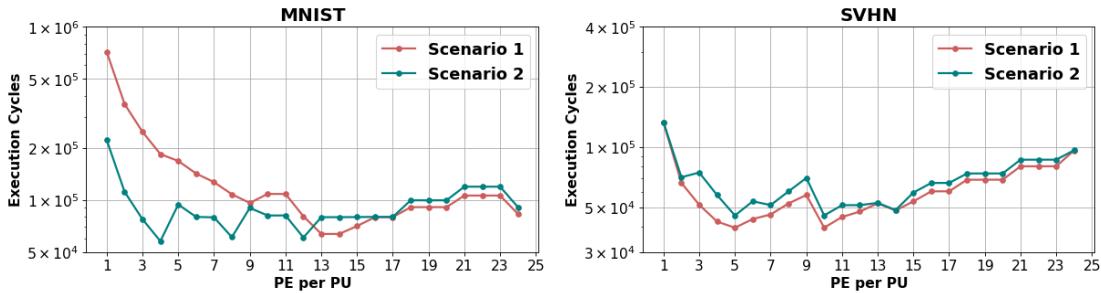

| Figure 4.5: Design space exploration for MNIST and SVHN benchmarks on <i>Xilinx Zynq-ZC702</i> FPGA. DeepFense finds the optimal configuration of PEs and PUs to best fit the DNN architecture and the available hardware resources. . . . .                                                           | 54 |

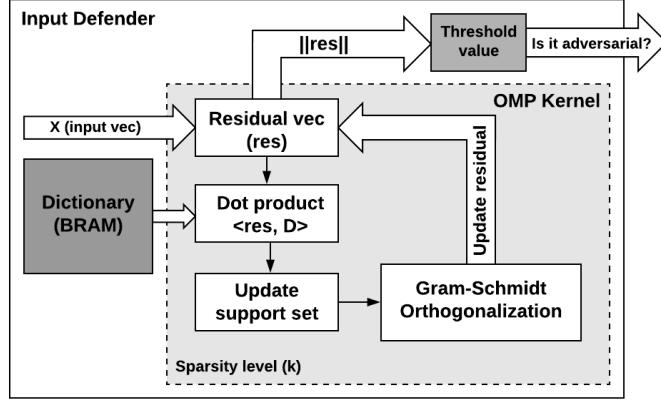

| Figure 4.6: Architecture of DeepFense input defender. . . . .                                                                                                                                                                                                                                          | 56 |

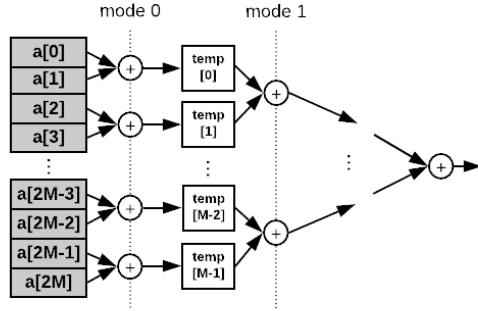

| Figure 4.7: Realization of the tree-based vector reduction algorithm. . . . .                                                                                                                                                                                                                          | 56 |

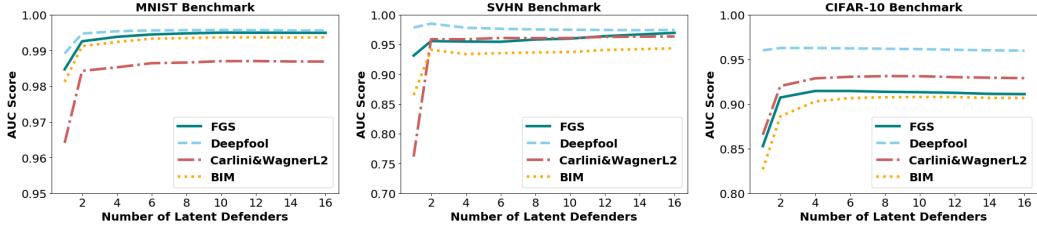

| Figure 4.8: AUC score versus the number of defender modules for MNIST, SVHN, and CIFAR-10 datasets. . . . .                                                                                                                                                                                            | 61 |

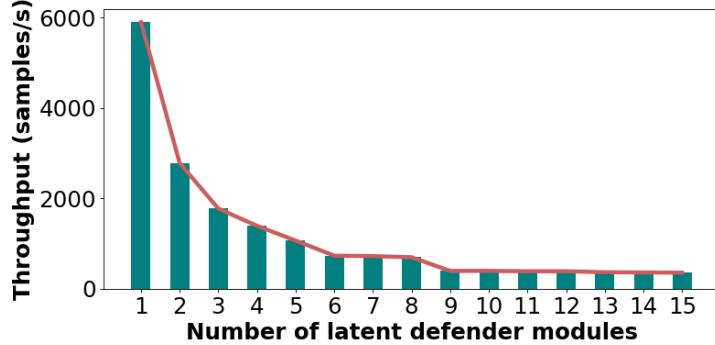

| Figure 4.9: Throughput of DeepFense with samples from the MNIST dataset, implemented on the <i>Xilinx Zync-ZC702</i> FPGA versus the number of instantiated defenders. . . . .                                                                                                                         | 62 |

|                                                                                                                                                                                                                                                   |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

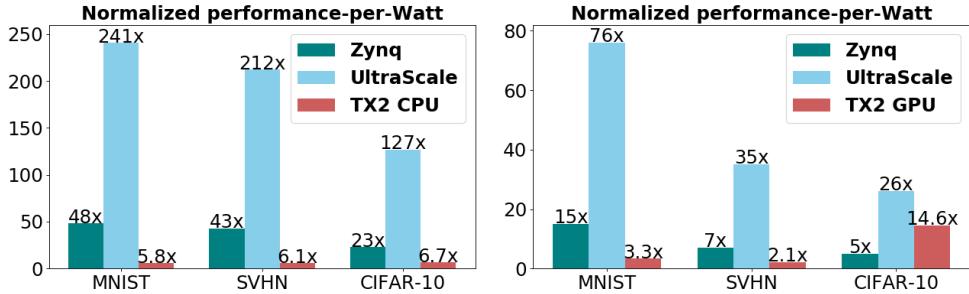

| Figure 4.10: Performance-per-Watt comparison with embedded CPU (left) and CPU-GPU (right) platforms. Reported values are normalized by the performance-per-Watt of <i>Jetson TK1</i> . . . . .                                                    | 63  |

| Figure 4.11: Example adversarial confusion matrix. . . . .                                                                                                                                                                                        | 64  |

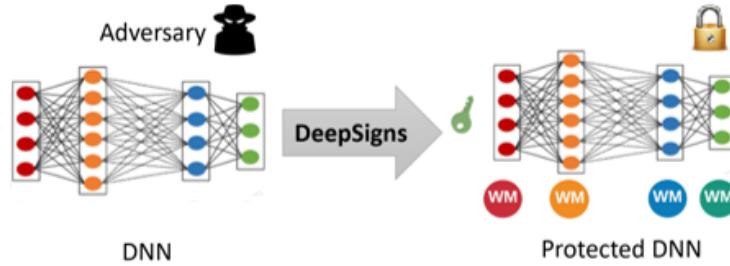

| Figure 5.1: DeepSigns is a systematic solution to protect the intellectual property of deep neural networks. . . . .                                                                                                                              | 70  |

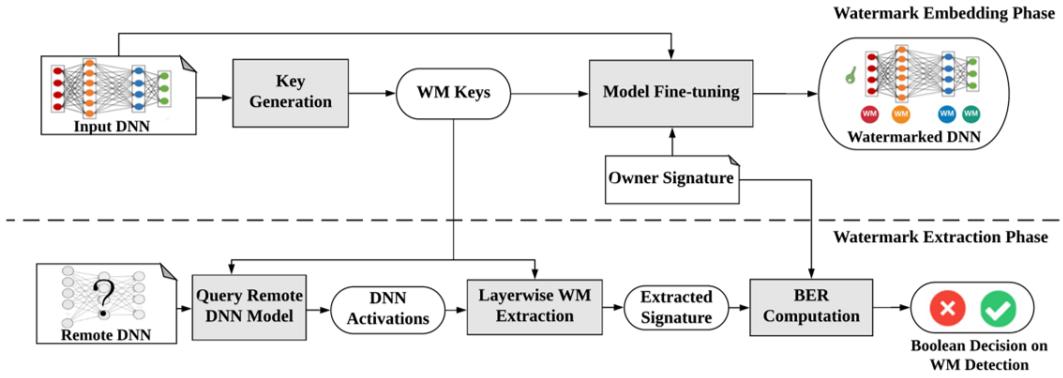

| Figure 5.2: Global flow of DeepSigns framework. . . . .                                                                                                                                                                                           | 72  |

| Figure 5.3: DeepSigns library usage and resource management for WM embedding and extracting in hidden layers. . . . .                                                                                                                             | 80  |

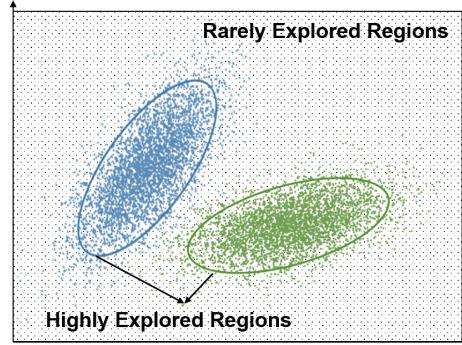

| Figure 5.4: Due to the high dimensionality of DNNs and limited access to labeled data, there are regions that are rarely explored. DeepSigns exploits this mainly unused regions for WM embedding while minimally affecting the accuracy. . . . . | 81  |

| Figure 5.5: Using DeepSigns library for WM embedding and extraction in the output layer. . . . .                                                                                                                                                  | 85  |

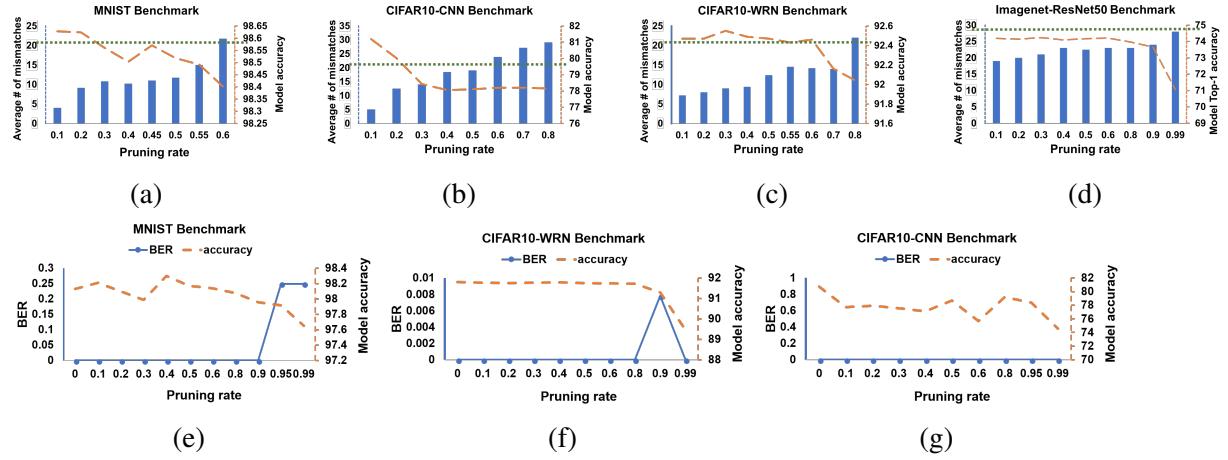

| Figure 5.6: Robustness against parameter pruning. . . . .                                                                                                                                                                                         | 89  |

| Figure 5.7: Integrity analysis of DeepSigns framework. . . . .                                                                                                                                                                                    | 91  |

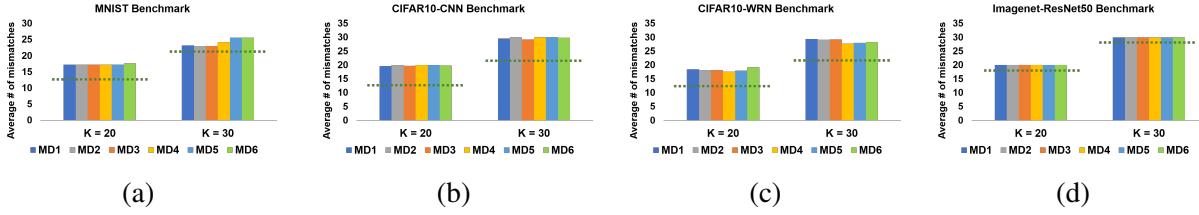

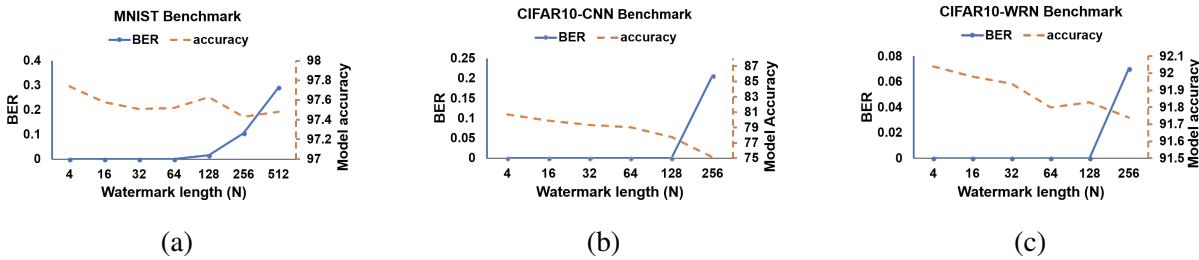

| Figure 5.8: There is a trade-off between the length of the WM signature (capacity) and the bit error rate of WM extraction. Embedding excessive amount of WM information impairs fidelity and reliability. . . . .                                | 91  |

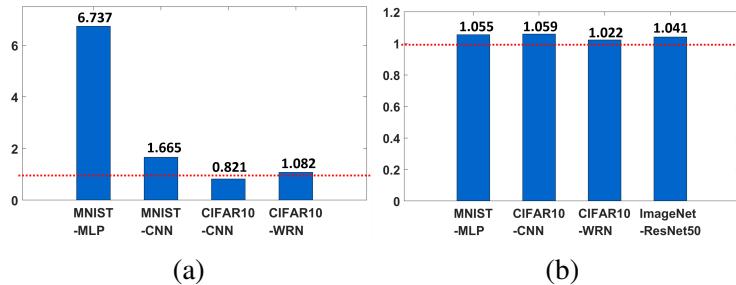

| Figure 5.9: Normalized watermark embedding runtime overhead in DeepSigns framework. . . . .                                                                                                                                                       | 92  |

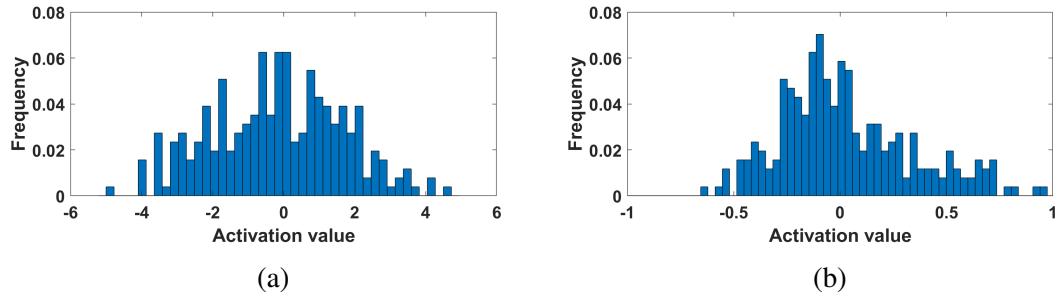

| Figure 5.10: Distribution of the activation maps for (a) marked and (b) unmarked models. DeepSigns preserves the intrinsic distribution while securely embedding the watermark information. . . . .                                               | 93  |

| Figure 6.1: Global flow of DeepSecure framework. . . . .                                                                                                                                                                                          | 100 |

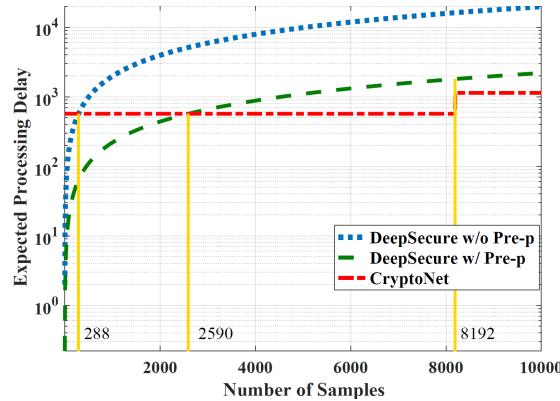

| Figure 6.2: Expected processing time from client's point of view as a function of data batch size in DeepSecure framework. . . . .                                                                                                                | 110 |

| Figure 7.1: Global flow of ReDCrypt framework. . . . .                                                                                                                                                                                            | 118 |

| Figure 7.2: Convolution operation can be mapped into matrix multiplication. . . . .                                                                                                                                                               | 121 |

| Figure 7.3: ReDCrypt system architecture on the server side. . . . .                                                                                                                                                                              | 122 |

| Figure 7.4: Schematic depiction of the tree-base multiplication. . . . .                                                                                                                                                                          | 125 |

| Figure 7.5: The high-level configuration and functionality of the parallel Garble circuit cores in segment 1 (MUX_ADD). . . . .                                                                                                                   | 127 |

| Figure 7.6: Logic operations performed in one Garble circuit core. . . . .                                                                                                                                                                        | 127 |

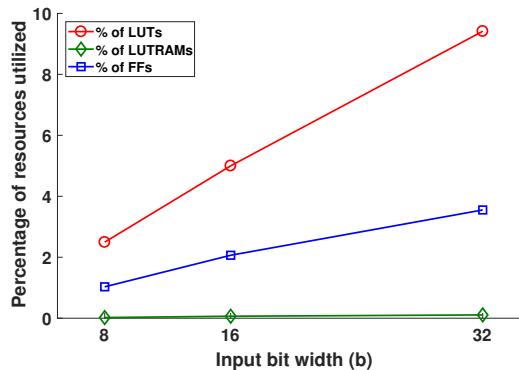

| Figure 7.7: Percentage resource utilization per MAC for different bit-widths. . . . .                                                                                                                                                             | 131 |

| Figure 8.1: Global flow of CausaLearn framework. CausaLearn empowers real-time analysis of time-series data with causal structure. . . . .                                                                                                        | 144 |

| Figure 8.2: High-level block diagram of Hamiltonian MCMC. . . . .                                                                                                                                                                                 | 149 |

| Figure 8.3: CausaLearn uses cyclic interleaving to facilitate concurrent load/store in performing matrix computations. . . . .                                                                                                                    | 152 |

| Figure 8.4: Facilitating matrix multiplication and dot product using tree structure. . . . .                                                                                                                                                      | 154 |

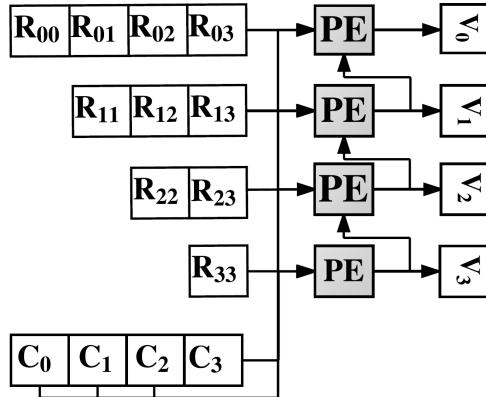

| Figure 8.5: Schematic depiction of back-substitution. . . . .                                                                                                                                                                                     | 155 |

|              |                                                                                                                                                         |     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 8.6:  | CausaLearn architecture for computing back-substitution. . . . .                                                                                        | 156 |

| Figure 8.7:  | Example data parallelism in CausaLearn matrix inversion unit. . . . .                                                                                   | 157 |

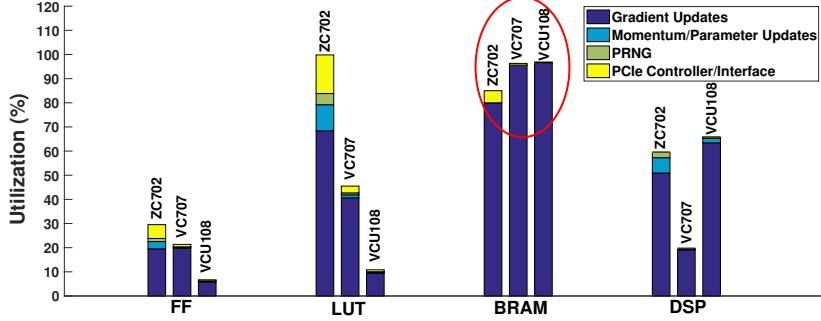

| Figure 8.8:  | Resource utilization of CausaLearn framework on different FPGA platforms. .                                                                             | 162 |

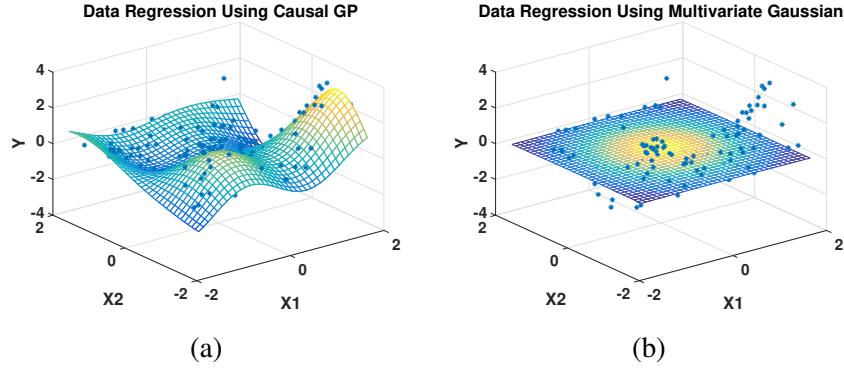

| Figure 8.9:  | Time-variant data analysis using MCMC samples by assuming causal GP prior (CausaLearn) versus i.i.d. assumption with multivariate Gaussian prior. .     | 164 |

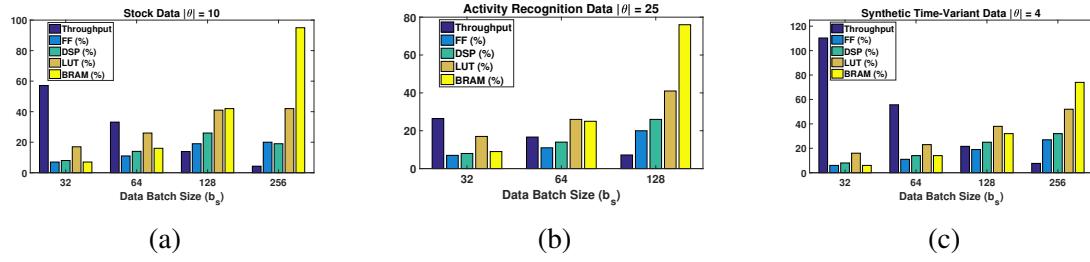

| Figure 8.10: | VC707 resource utilization and system throughput per H_MCMC unit as a function of data batch size. . . . .                                              | 165 |

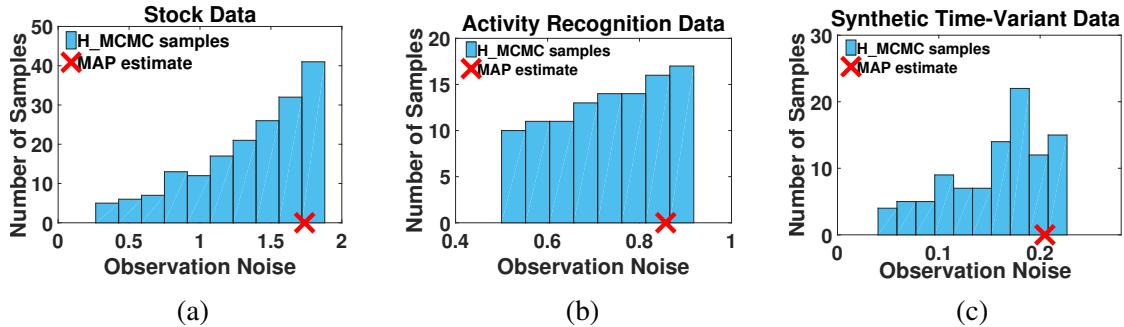

| Figure 8.11: | Example CausaLearn's posterior distribution samples. The red cross sign on each graph demonstrates the maximum a posterior estimate in each experiment. | 165 |

## LIST OF TABLES

|            |                                                                                                                                                                                         |     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1: | Commonly layers employed in deep neural networks. . . . .                                                                                                                               | 15  |

| Table 2.2: | Markov Chain Monte Carlo (MCMC) methodologies commonly used for analyzing graphical Bayesian networks. . . . .                                                                          | 18  |

| Table 3.1: | Local Computation and Communication Costs. . . . .                                                                                                                                      | 33  |

| Table 3.2: | Deep3 pre-processing overhead. . . . .                                                                                                                                                  | 36  |

| Table 3.3: | Performance improvement achieved by Deep3 over prior-art deep learning approach. . . . .                                                                                                | 37  |

| Table 4.1: | Motivational example. We compare the MRR methodology against prior-art works in the face of adaptive white-box adversarial attacks. . . . .                                             | 47  |

| Table 4.2: | Architectures of evaluated victim deep neural networks. . . . .                                                                                                                         | 60  |

| Table 4.3: | Adversarial attacks' hyper-parameters. . . . .                                                                                                                                          | 60  |

| Table 5.1: | Requirements for an effective watermarking of deep neural networks. . . . .                                                                                                             | 73  |

| Table 5.2: | Benchmark neural network architectures used for evaluating DeepSigns framework. . . . .                                                                                                 | 87  |

| Table 5.3: | DeepSigns is robust against model fine-tuning attack. . . . .                                                                                                                           | 89  |

| Table 5.4: | DeepSigns is robust against overwriting attack. The reported number of mismatches is the average value of 10 runs for the same model using different WM key sets. . . . .               | 90  |

| Table 5.5: | Robustness comparison against overwriting attacks. . . . .                                                                                                                              | 95  |

| Table 5.6: | Integrity comparison between DeepSigns and prior work. . . . .                                                                                                                          | 95  |

| Table 6.1: | Garble circuit Computation and Communication Costs for realization of a deep neural network. . . . .                                                                                    | 102 |

| Table 6.2: | Number of XOR and non-XOR gates for each operation of DL networks. . . . .                                                                                                              | 106 |

| Table 6.3: | Number of XOR and non-XOR gates, communication, computation time, and overall execution time for different benchmarks without involving the data and DL network pre-processing. . . . . | 108 |

| Table 6.4: | Number of XOR and non-XOR gates, communication, computation time, and overall execution time for different benchmarks after considering the pre-processing steps. . . . .               | 109 |

| Table 6.5: | Communication and computation overhead per sample in DeepSecure vs. CryptoNet [GBDL <sup>+</sup> 16] for benchmark 1. . . . .                                                           | 109 |

| Table 7.1: | Resource usage of one MAC unit. . . . .                                                                                                                                                 | 131 |

| Table 7.2: | Throughput Comparison of ReDCrypt with state-of-the-art GC frameworks. . . . .                                                                                                          | 132 |

| Table 7.3: | Number of XOR and non-XOR gates, amount of communication and computation time for each benchmark evaluated by ReDCrypt framework. . . . .                                               | 133 |

| Table 7.4: | Ridge Regression Runtime Improvement. . . . .                                                                                                                                           | 135 |

|                                                                                                                                                                                   |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 8.1: CausaLearn memory and runtime characterization. . . . .                                                                                                                | 158 |

| Table 8.2: Relative runtime/energy improvement per H_MCMC iteration achieved by CausaLearn on different platforms compared to a highly-optimized software implementation. . . . . | 163 |

## ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere appreciation to my advisor Prof. Farinaz Koushanfar for her priceless support, encouragement, and guidance. Her dedication, fondness, and motivation towards doing novel research, as well as exceptional care for her students have taught me invaluable lessons and greatly influenced my life at both academic and personal levels. I will always be candidly grateful for all her advice and support.

I would like to thank my committee members, Prof. Hadi Esmaeilzadeh, Prof. Tara Javidi, Prof. Truong Nguyen, Prof. Bhaskar Rao, and Prof. Tajana Simunic Rosing for taking the time to be part of my committee and for their valuable comments and suggestions. I would also like to sincerely thank my mentors at Microsoft Research, Dr. Doug Burger and Dr. Eric Chung, for their invaluable support and guidance. Working with them was a great opportunity for me to explore the link between research and building first-class technologies.

My experience of Ph.D. was made a lot more delightful because of the brilliant people I was lucky enough to get to know them and/or collaborate with them. In particular, I would like to thank Dr. Azalia Mirhoseini, Dr. Ebrahim Songhori, Mojan Javaheripi, Huili Chen, Mohammad Samragh, Siam Umar Hussain, Mohammad Ghasemzadeh, Salar Yazdjerdi, Fang Lin, Somayeh Imani, Amir Yazdanbakhsh, and Bahar Salimian for all their helps and the happy times we had together. Last but not the least, I wish to express my profound admiration and gratitude to my beloved parents and brothers for their endless love, for believing in me, for inspiring me to dream big and work hard to follow them, and for showing me constant support even when we were physically far apart.

The material in this dissertation is based on the following papers which are either published, under review, or in preparation for submission.

Chapter 1, in part, (i) has been published at IEEE Security and Privacy (S&P) Magazine 2018 as Bita Darvish Rouhani, Mohammad Samragh, Tara Javidid, and Farinaz Koushanfar “Safe Machine Learning and Defeating Adversarial Attacks”, and (ii) has been submitted to

Communication of ACM as Bita Darvish Rouhani, Azalia Mirhoseini, and Farinaz Koushanfar “Succinct Training and Execution of Deep Learning on Edge Devices: Depth-First Distributed Graph Traversal, Data Embedding, and Resource Parallelism”. The dissertation author was the primary author of this material.

Chapter 2 and 3, in part, has been published at (i) the Proceedings of 2017 International Design Automation Conference (DAC) and appeared as: Bita Darvish Rouhani, Azalia Mirhoseini, and Farinaz Koushanfar “Deep3: Leveraging Three Levels of Parallelism for Efficient Deep Learning”, and (ii) the Proceedings of the 2016 International Symposium on Low Power Electronics and Design (ISLPED) as: Bita Darvish Rouhani, Azalia Mirhoseini, and Farinaz Koushanfar “Delight: Adding energy dimension to deep neural networks”. The dissertation author was the primary author of this material.

Chpater 4, in part, has been published at (i) the Proceedings of 2018 International Conference On Computer Aided Design (ICCAD) and appeared as: Bita Darvish Rouhani, Mohammad Samragh, Mojan Javaheripi, Tara Javidid, and Farinaz Koushanfar “DeepFense: Online Accelerated Defense Against Adversarial Deep Learning”, and (ii) IEEE Security and Privacy (S&P) Magazine 2018 as ita Darvish Rouhani, Mohammad Samragh, Tara Javidid, and Farinaz Koushanfar “Safe Machine Learning and Defeating Adversarial Attacks”. The dissertation author was the primary author of this material.

Chapter 5, in part, has been published at arXiv preprint arXiv:1804.00750, 2018 as: Bita Darvish Rouhani, Huili Chen, and Farinaz Koushanfar “Deepsigns: A generic watermarking framework for ip protection of deep learning models”. The dissertation author was the primary author of this material.

Chapter 6, in part, has been published at the Proceedings of the 2018 ACM International Symposium on Design Automation Conference (DAC) and appeared as: Bita Darvish Rouhani, Sadegh Riazi, and Farinaz Koushanfar “DeepSecure: Scalable Provably-Secure Deep Learning”. The dissertation author was the primary author of this material.

Chapter 2 and 7, in part, has been published at ACM Transactions on Reconfigurable Technology and Systems (TRETS) 2018 as: Bita darvish Rouhani, Siam U Hussain, Kristin Lauter, and Farinaz Koushanfar “ReDCrypt: Real-Time Privacy-Preserving Deep Learning Inference in Clouds Using FPGAs” and the Proceedings of the 2018 ACM International Symposium on Design Automation Conference (DAC) and appeared as: Siam U Hussain, Bita Darvish Rouhani, Mohammad Ghasemzadeh, and Farinaz Koushanfar “MAXelerator: FPGA accelerator for privacy preserving multiply-accumulate (MAC) on cloud servers”. The dissertation author was the primary author of the ReDCrypt paper and the secondary author of MAXelerator paper. ReDCrypt is particularly designed for deep learning models and MAXelerator is a generic privacy preserving matrix multiplication framework that is designed in collaboration with Siam U Hussain.

Chapter 2 and 8, This chapter, in part, has been published at the Proceedings of the 2018 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA) and appeared as: Bita Darvish Rouhani, Mohammad Ghasemzadeh, and Farinaz Koushanfar “CausaLearn: Automated Framework for Scalable Streaming-based Causal Bayesian Learning using FPGAs”. The dissertation author was the primary author of this material.

This dissertation was supported, in parts, by the ONR (N00014-11-1-0885), NSF (CNS-1619261), NSF TrustHub (1649423), and Microsoft Research Ph.D. fellowship grants.

## VITA

|           |                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| 2013      | Bachelor of Science in Electrical Engineering, Sharif University of Technology, Tehran, Iran                                    |

| 2015      | Master of Science in Computer Engineering, Rice University, Houston, Texas                                                      |

| 2015-2018 | Graduate Research Assistant, University of California San Diego, La Jolla, California                                           |

| 2018      | Doctor of Philosophy in Electrical Engineering (Computer Engineering), University of California San Diego, La Jolla, California |

## PUBLICATIONS

**B. Rouhani**, M. Ghasemzadeh, and F. Koushanfar. “Automated scalable framework for streaming-based causal Bayesian learning using FPGAs.” In 26th ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA), 2018.

**B. Rouhani**, M. Samragh, T. Javidi, and F. Koushanfar. “Safe Machine Learning and Defeating Adversarial Attacks.” IEEE Security and Privacy (S&P) magazine, 2018.

**B. Rouhani**, M. Samragh, M. Javaheripi, T. Javidi, and F. Koushanfar. “DeepFense: Online Accelerated Defense Against Adversarial Deep Learning.” International Conference On Computer Aided Design (ICCAD), 2018.

**B. Rouhani**, Siam Umar Hussain, Kristin Lauter, and Farinaz Koushanfar. “ReDCrypt: Real-Time Privacy Preserving Deep Learning Using FPGAs.” ACM Transactions on Reconfigurable Technology and Systems (TRETS), 2018.

**B. Rouhani**, H. Chen, and F. Koushanfar. “DeepSigns: A Generic Framework for Watermarking and IP Protection of Deep Learning Models.” ArXiv Preprint arXiv:1804.00750, 2018.

H. Chen, **B. Rouhani**, and F. Koushanfar. “DeepMarks: A Digital Fingerprinting Framework for Deep Neural Networks.” ArXiv Preprint arXiv:1804.03648, 2018.

S. Hussain, **B. Rouhani**, M. Ghasemzadeh, and F. Koushanfar. “MAXelerator: FPGA Accelerator for Privacy Preserving Multiply-Accumulate (MAC) on Cloud Servers.” In Proceedings of Design Automation Conference (DAC), 2018.

M. Ghasemzadeh, F. Lin, **B. Rouhani**, F. Koushanfar, and K. Huang. “AgileNet: Lightweight Dictionary-based Few-shot Learning.” ArXiv Preprint 1805.08311, 2018.

**B. Rouhani**, A. Mirhoseini, and F. Koushanfar. “Succinct Training and Execution of Deep Learning on Edge Devices: Depth-First Distributed Graph Traversal, Data Embedding, and Resource Parallelism.” Under Review in Communication ACM Magazine, 2018.

**B. Rouhani**, S. Riazi, and F. Koushanfar. “DeepSecure: Scalable Provably-Secure Deep Learning.” In Proceedings of Design Automation Conference (DAC), 2018.

S. Riazi, **B. Rouhani**, and F. Koushanfar. “Privacy Concerns in Deep Learning.” IEEE Security and Privacy (S&P) magazine, 2018.

**B. Rouhani**, A. Mirhoseini, and F. Koushanfar. “Deep3: Leveraging Three Levels of Parallelism for Efficient Deep Learning.” In Proceedings of Design Automation Conference (DAC), 2017.

**B. Rouhani**, A. Mirhoseini, and F. Koushanfar. “RISE: An Automated Framework for Real-Time Intelligent Video Surveillance on FPGA.” ACM Transactions on Embedded Computing Systems (TECS), 2017.

A. Mirhoseini, **B. Rouhani**, E. Songhori, and F. Koushanfar. “ExtDict: Extensible Dictionaries for Data- and Platform-Aware Large-Scale Learning.” In Proceedings of International Parallel & Distributed Processing Symposium (IPDPS) ParLearning workshop, 2017.

**B. Rouhani**, M. Ghasemzadeh, and F. Koushanfar. “Real-time Causal Internet Log Analytics by HW/SW/Projection Co-design.” Hardware Demo in Proceedings of IEEE International Symposium on Hardware Oriented Security and Trust (HOST), 2017.

**B. Rouhani**, A. Mirhoseini, and F. Koushanfar. “TinyDL: Just-in-Time Deep Learning Solution for Constrained Embedded Systems.” In Proceedings of International Symposium on Circuits & Systems (ISCAS), 2017.

**B. Rouhani**, A. Mirhoseini, and F. Koushanfar. “DeLight: Adding Energy Dimension to Deep Neural Networks.” In Proceedings of International Symposium on Low Power Electronics and Design (ISLPED), 2016.

**B. Rouhani**, A. Mirhoseini, E. Songhori, and F. Koushanfar. “Automated Real-Time Analysis of Streaming Big and Dense Data on Reconfigurable Platforms.” ACM Transactions on Reconfigurable Technology and Systems (TRETS), 2016.

**B. Rouhani**, A. Mirhoseini, and F. Koushanfar. “Going Deeper than Deep Learning for Massive Data Analytics under Physical Constraints.” In Proceedings of International Conference on Hardware/Software Co-design and System Synthesis (CODES+ISSS), 2016.

A. Mirhoseini, **B. Rouhani**, E. Songhori, and F. Koushanfar. “Chime: Checkpointing Long Computations on Intermittently Energized IoT Device.” IEEE Transactions on Multi-Scale Computing Systems (TMSCS), 2016.

A. Mirhoseini, **B. Rouhani**, E. Songhori, and F. Koushanfar. “PerformML: Performance Optimized Machine Learning by Platform and Content Aware Customization.” In Proceedings of Design Automation Conference (DAC), 2016.

**B. Rouhani**, E. Songhori, A. Mirhoseini, and F. Koushanfar. “SSketch: An Automated Framework for Streaming Sketch-based Analysis of Big Data on FPGA.” Field-Programmable Custom Computing Machines (FCCM), 2015.

A. Mirhoseini, E. Songhori, **B. Rouhani**, and F. Koushanfar. “Flexible Transformations for Learning Big Data.” Short Paper, ACM Special Interest Group for the Computer Systems Performance Evaluation Conference, (SIGMETRICS), 2015.

## ABSTRACT OF THE DISSERTATION

### **Succinct and Assured Machine Learning: Training and Execution**

by

Bita Darvish Rouhani

Doctor of Philosophy in Electrical Engineering (Computer Engineering)

University of California, San Diego, 2018

Professor Farinaz Koushanfar, Chair

Contemporary datasets are rapidly growing in size and complexity. This wealth of data is providing a paradigm shift in various key sectors including defense, commercial, and personalized computing. Over the past decade, machine learning and related fields have made significant progress in designing rigorous algorithms with the goal of making sense of this large corpus of available data. Concerns over physical performance (runtime and energy consumption), reliability (safety), and ease-of-use, however, pose major roadblocks to the wider adoption of machine learning techniques. To address the aforementioned roadblocks, a popular recent line of research is focused on performance optimization and machine learning acceleration via hardware/software co-design and automation. This thesis advances the state-of-the-art in this growing field by

advocating a *holistic automated co-design* approach which involves not only *hardware* and *software* but also the *geometry of the data* and *learning model* as well as the *security requirements*.

My key contributions include:

- Co-optimizing graph traversal, data embedding, and resource allocation for succinct training and execution of Deep Learning (DL) models. The resource efficiency of my end-to-end automated solutions not only enables compact DL training/execution on edge devices but also facilitates further reduction of the training time and energy spent on cloud data servers.

- Characterizing and thwarting adversarial subspace for robust and assured execution of DL models. I build a holistic hardware/software/algorithm co-design that enables just-in-time defense against adversarial attacks. My proposed countermeasure is robust against the strongest adversarial attacks known to date without violating the real-time response requirement, which is crucial in sensitive applications such as autonomous vehicles/drones.

- Proposing the first efficient resource management framework that empowers coherent integration of robust digital watermarks/fingerprints into DL models. The embedded digital watermarks/fingerprints are robust to removal and transformation attacks and can be used for model protection against intellectual property infringement.

- Devising the first reconfigurable and provably-secure framework that simultaneously enables accurate and scalable DL execution on encrypted data. The proposed framework supports secure streaming-based DL computation on cloud servers equipped with FPGAs.

- Developing the first scalable framework that enables real-time approximation of multi-dimensional probability density functions for causal Bayesian analysis. The proposed solution adaptively fine-tunes the underlying latent variables to cope with the data dynamics as it evolves over time.

# Chapter 1

## Introduction

Computers and sensors generate data at an unprecedented rate. Analyzing massive and densely-correlated data is an omnipresent trend on different computing platforms. There are (at least) two major sets of challenges that need to be addressed simultaneously to build a learning system that is both sustainable and trustworthy. One set of hurdles is related to the physical resources and/or application-specific constraints such as real-time requirements, available energy, and/or memory bandwidth. The other set of challenges arises due to the entanglement of high-dimensional data. On the one hand, this data entanglement makes it necessary to go beyond traditional linear or polynomial analytics to reach a certain level of accuracy. On the other hand, the complexity of contemporary machine learning models makes them prone to certain degree of nuisance variables that are not necessarily the key features used by human brains. These non-intuitive nuisance variables, in turn, can be leveraged by adversaries to fool the underlying machine learning agent. As such, it is critical to also assure model robustness in the face of adversarial attacks while minimally affecting the underlying system performance.

This thesis addresses the aforementioned two critical aspects of emerging computing scenarios by designing and building holistic solutions and tools that are simultaneously co-optimized for the underlying data geometry, coarse-grained model parallelism, hardware characteristics, and

security requirements (Figure 1.1). My holistic solutions provide a promising avenue to improve the performance of existing cloud-based services. They also unlock new capabilities and services (e.g., significantly longer battery life) for embedded Internet-of-Things (IoT) devices.

**Figure 1.1:** Research overview. My work enables the next generation of cyber-physical applications by devising holistic computing frameworks that are simultaneously optimized for the underlying data, learning algorithm, hardware, and security requirements.

My research work is focused on performance optimization for two of the state-of-the-art classes of machine learning namely *Deep Learning (DL)* and *causal Bayesian analysis*. In this section, I highlight the challenges that arise while solving these problems and review prior works. I then discuss my proposed holistic solutions and describe their versatility and broader impact.

## 1.1 Resource-Efficient and Trusted Deep Learning

Deep learning has become the key methodology for achieving the state-of-the-art accuracy by moving beyond traditional linear or polynomial analytics [DY14]. Despite DL's powerful learning capability, the computational overhead associated with DL methods has hindered their applicability to resource-constrained settings. Examples of such settings range from embedded devices to data centers where physical viability (e.g., runtime and energy efficiency) is a standing challenge. In the following, I first discuss my work on devising resource-efficient DL systems. I then discuss my work to promote reliability and user privacy in DL applications.

### 1.1.1 Succinct Training and Execution of Deep Neural Networks

Deep learning models are conventionally trained on big data servers. In applications where DL execution on the edge is needed, the trained models are compacted to fit within the constraints of the executing device. Several previous works have demonstrated a significant amount of redundancy in DL models, which allows compacting of pre-trained models on edge devices without considerable loss of accuracy. However, training/fine-tuning of models on large cloud servers assumes constant access to high-performance computing platforms and fast connectivity. Furthermore, in applications where data is collected on edge devices, both the sensor data and model have to be transferred over a remote connection. This would lead to exposure of the data and model in plaintext, a serious security concern for sensitive tasks.

I have introduced, realized, and automated the first resource-aware deep learning framework (called Deep3) that achieves orders of magnitude performance efficiency for training and execution of DL networks on various families of platforms including embedded GPUs, and FPGAs, as well as distributed multi-core CPUs [RMK17a, RMK16]. The rationale in this work is that models which inherently have a high degree of redundancy can be originally trained to be compact and not include unnecessary repetitive parts. Such an approach not only introduces a paradigm shift in model building on edge devices without the overhead of communicating with the cloud but also enables additional reduction of the training time and energy spent on cloud data servers. Even execution time and energy efficiency could be significantly revamped compared to conventional post-facto compacting of large redundant models.

Figure 1.2 compares existing deep learning frameworks in terms of their high-level characteristics. More specifically, the state-of-the-art frameworks for DL optimization and acceleration can be divided into three main categories.

- **Data and algorithm optimization.** Data scientists and engineers have primarily focused on DL complexity reduction from an algorithmic/data point of view with limited or no attention to the target hardware characteristics [CHW<sup>+</sup>13, CSAK14, DCM<sup>+</sup>12]. Algorithmic and data

|                             | DL Execution | DL Training | DL Model Parallelism | Data Subspace Parallelism | HW/SW Co-design | Non-recurring Engineering Cost | Multi-platform Support |

|-----------------------------|--------------|-------------|----------------------|---------------------------|-----------------|--------------------------------|------------------------|

| <b>Deep3 (DAC'17)</b>       | ✓            | ✓           | ✓                    | ✓                         | ✓               | ✓                              | ✓                      |

| <b>DistBelief (NIPS'12)</b> | ✓            | ✓           | ✓                    | ✗                         | ✗               | ✗                              | ✗                      |

| <b>Adam (OSDI'14)</b>       | ✓            | ✓           | ✓                    | ✗                         | ✗               | ✓                              | ✗                      |

| <b>DnnWeaver (Micro'16)</b> | ✓            | ✗           | ✗                    | ✗                         | ✓               | ✓                              | ✗                      |

| <b>EIE (ISCA'16)</b>        | ✓            | ✗           | ✗                    | ✗                         | ✓               | ✗                              | ✗                      |

| <b>FP-DNN (FPGA'17)</b>     | ✓            | ✗           | ✗                    | ✗                         | ✓               | ✓                              | ✗                      |

| <b>Xnor-Net (ECCV'16)</b>   | ✓            | ✗           | ✗                    | ✗                         | ✗               | ✗                              | ✗                      |

| <b>NetAdapt (ArXiv'18)</b>  | ✓            | ✗           | ✗                    | ✗                         | ✓               | ✓                              | ✗                      |

**Figure 1.2:** Comparison of several state-of-the-art deep learning frameworks in terms of their high-level characteristics and features.

optimization without insight from underlying hardware constraints, however, are not sufficient for the succinct realization of DL models. As an example, consider the SqueezeNet network in which the number of weights in the AlexNet model is reduced by a factor of 50 with the goal of an efficient DL inference [IHM<sup>+</sup>16]. This work and similar DL pruning techniques have been developed based on an implicit assumption that fewer weights result in a more efficient realization. This assumption is not generic across various hardware platforms. In fact, as shown on several embedded devices, SqueezeNet takes approximately 30% more energy compared to the original AlexNet [Mol16, YCS16]. This is particularly because, although a smaller number of weights in a neural network directly reduces the pertinent memory storage requirement, it does not necessarily translate to less energy consumption (i.e., more battery life). In such cases, the size of feature maps and memory access pattern are the dominant factors for energy cost on most embedded platforms. Therefore, it is imperative to include platform-awareness in algorithms to adjust the performance for the target hardware with minimal involvement of human experts.

■ **Hardware optimization and acceleration.** The development of domain-customized hardware accelerated solutions for efficient implementation of DL models is a key approach taken by several computer engineering researchers [ZLS<sup>+</sup>15, JGD<sup>+</sup>14]. Although this line of work has demonstrated significant improvement in deployment of specific DL applications, it has

several restrictions mainly stem from the inflexibility of custom solutions for the realization of other applications. Model and content optimization is often data-dependent and, as such, the methodologies for custom model compaction do not transform into other domains. We believe that by automatic integration of the algorithm and data subspace geometries one can take full advantage of potential opportunities for succinct learning.

■ **Algorithm, data, and hardware co-optimization.** Designing automated hardware-aware graph traversal and data embeddings could highly benefit the physical performance of the underlying DL task. I propose Deep3, an automated system that simultaneously leverages three levels of parallelism, namely, data, model, and hardware, for succinct training and execution of neural networks in resource-constrained settings. In particular, I introduce a new extensible and resource-aware graph traversal methodology that (i) allows time multiplexing of the limited resources on the edge and (ii) balances the computation and communication workload for distributed training of large-scale DL models. Deep3 reports the first instance of DL training on embedded GPUs with orders of magnitude runtime and energy improvement achieved by holistic customization to the limits of the hardware resources, data embedding, and DL models [RMK17a, RMK16]. More recently, the NetAdapt framework [YHC<sup>+</sup>18] is proposed by Google, in which automated customization is performed to adjust the target DL model in accordance with target hardware for efficient DL execution. Unlike Deep3, NetAdapt does not provide DL training.

### 1.1.2 Assured Deep Neural Networks Against Adversarial Attacks

Reliability and safety consideration is the biggest obstacle to the wide-scale adoption of emerging learning algorithms in sensitive scenarios such as intelligent transportation, health-care, warfare, and financial systems. Although deep learning models deliver high accuracy in conventional settings with limited simulated input samples, recent research in adversarial DL has shed light on the unreliability of their decisions in real-world scenarios. For instance, consider a traffic sign classifier used in self-driving cars. Figure 1.3 shows an example adversarial sample

where the attacker carefully adds imperceptible perturbation to the input image to mislead the employed DL model, and thus, jeopardizes the safety of the vehicle.

**Figure 1.3:** The left image is a legitimate “stop” sign sample that is classified correctly by an ML model. The right image, however, is an adversarial input crafted by adding a particular perturbation that makes the same model classify it as a “yield” sign.

I introduce, implement, and automate a novel countermeasure called Modular Robust Redundancy (MRR) to thwart the potential adversarial space and significantly improve the reliability of a victim DL model [RSJ<sup>+</sup>18, RSJK18a]. Unlike prior defense strategies, MRR methodology is based on unsupervised learning, meaning that no particular adversarial sample is leveraged to build/train the modular redundancies. Instead, my unsupervised learning methodology leverages the structure of the built model and characterizes the distribution of the high dimensional space in the training data. Adopting an unsupervised learning approach, in turn, ensures that the proposed detection scheme can be generalized to a wide class of adversarial attacks. Combined with my resource-efficient DL implementation tool, I build a holistic end-to-end DL system that not only is succinct and accurate but also its integrity is assured against adversarial attacks.

Adversarial samples have already exposed the vulnerability of DL models to malicious attacks; thereby undermining the integrity of autonomous systems built upon deep learning. It is critical to ensure the reliability of DL models in the early development stage instead of looking back with regret when the machine learning systems are compromised by adversaries. My work, in turn, empowers coherent integration of safety consideration into the design process of DL models while minimally affecting the pertinent physical performance in terms of runtime (latency) and/or energy consumption.

### 1.1.3 Watermarking of Deep Neural Networks

Training a highly accurate DL model requires: (i) having access to a massive collection of mostly proprietary labeled data that furnishes comprehensive coverage of potential scenarios in the target application; (ii) allocating substantial computing resources to fine-tune the underlying model topology (i.e., type and number of hidden layers), hyper-parameters (i.e., learning rate, batch size, etc.), and weights to obtain the most accurate model. Given the costly process of DL training, models are typically considered to be the Intellectual Property (IP) of the model builder.

Model protection against IP infringement is particularly important to preserve the competitive advantage of the owner and ensure the receipt of continuous query requests from clients. Embedding digital watermarks into DL models is a key enabler for reliable technology transfer. Digital watermarks have been immensely leveraged over the past decade to protect the ownership of multimedia and video content, as well as functional artifacts such as digital integrated circuits [FK04, HK99, QP07, CKLS97, Lu04]. Extension of watermarking techniques to DL networks, however, is still in its infancy to enable reliable model distribution. Moreover, adding digital watermarks further presses the already constrained memory for DL training. As such, efficient resource management to minimize the overhead of watermarking is a standing challenge.

Authors in [UNSS17, NUSS18] propose an  $N$ -bit ( $N > 1$ ) watermarking approach for embedding the IP information in the *static* content (i.e., weight matrices) of convolutional neural networks. Although this work provides a significant leap as the first attempt to watermark DL networks, it poses (at least) two limitations: (i) It incurs a bounded watermarking capacity due to the use of the static content of the model (weights) as opposed to using dynamic content (activations). The weights of a neural network are invariable (static) during the execution phase, regardless of the data passing through the model. The activations, however, are dynamic and both *data- and model-dependent*. We argue that using activations (instead of weights) provides more flexibility for watermarking. (ii) It is not robust against attacks such as overwriting the original embedded watermark by a third party. As such, the original watermark can be removed by an

adversary that is aware of the watermarking method used by the model owner.

More recent studies in [MPT17, ABC<sup>+</sup>18] propose 1-bit watermarking methodologies for deep learning models. These approaches are built upon model boundary modification and the use of random adversarial samples that lie near decision boundaries. Adversarial samples are known to be statistically unstable, meaning that adversarial samples crafted for a model are not necessarily misclassified by another network [GMP<sup>+</sup>17, RSJK18b]. Therefore, even though the proposed approaches in [MPT17, ABC<sup>+</sup>18] yield a high watermark detection rate (true positive rate), they are also too sensitive to hyper-parameter tuning and usually lead to a high false alarm rate. Note that false ownership proofs jeopardize the integrity of the proposed watermarking methodology and render the use of watermarks for IP protection ineffective.

I propose DeepSigns, the first end-to-end IP protection framework that enables developers to systematically insert digital watermarks in the pertinent DL model before distributing the model. DeepSigns is encapsulated as a high-level wrapper that can be leveraged within common deep learning frameworks including TensorFlow, PyTorch, and Theano. Unlike prior works that directly embed the watermark information in the static content (weights) of the pertinent model, DeepSigns works by embedding an arbitrary  $N$ -bit ( $N \geq 1$ ) string into the probability density function (pdf) of the activation maps in various layers of a deep neural network. Our proposed watermarking methodology is simultaneously *data- and model-dependent*, meaning that the watermark information is embedded in the dynamic content of the DL network and can only be triggered by passing specific input data to the model. DeepSigns' methodology can demonstrably withstand various removal and transformation attacks, including model pruning, model fine-tuning, and watermark overwriting. Figure 1.4 provides a high-level comparison between the state-of-the-art DL watermarking frameworks. As we demonstrate in [CRK18] DeepSigns' methodology can be extended for efficient DL fingerprinting as well.

|                      | DNN Watermarking |              |                         |                    |             |           |                       |

|----------------------|------------------|--------------|-------------------------|--------------------|-------------|-----------|-----------------------|

|                      | Output Layer     | Hidden Layer | Resource Management API | Data & Model Aware | Reliability | Integrity | Capacity              |

| DeepSigns            | ✓                | ✓            | ✓                       | ✓                  | ✓           | ✓         | N-bit with $N \geq 1$ |

| Uchida et al. (2017) | ✗                | ✓            | ✗                       | ✗                  | ✓           | ✓         | N-bit with $N \geq 1$ |

| Merrer&Perez (2017)  | ✓                | ✗            | ✗                       | ✗                  | ✓           | ✗         | 1-bit                 |

| Adi, et al. (2018)   | ✓                | ✗            | ✗                       | ✗                  | ✓           | ✗         | 1-bit                 |

**Figure 1.4:** High-level comparison between state-of-the-art watermarking frameworks for deep neural networks. DeepSigns’ framework is significantly more robust against removal and transformation attacks, including model pruning, model fine-tuning, and watermark overwriting. DeepSigns’ highly-optimized resource management tool, in turn, enables efficient training watermarked neural networks with an extra overhead as low as 2.2%.

### 1.1.4 Privacy-Preserving Deep Learning

Deep learning models are increasingly incorporated into the *cloud business* to improve the functionality (e.g., accuracy) of the service. A complicating factor in the rush to adopt DL as a cloud service is the data and model privacy. On the one hand, DL models are usually trained by allocating significant computational resources to process massive amounts of training data. As such, the trained models are considered an intellectual property of companies which require confidentiality to preserve the competitive advantage and ensure receiving continuous query requests by clients. On the other hand, clients do not desire to send their private data (e.g., location or financial input) in plain text to cloud servers due to the risk of information leakage.

To incorporate deep learning into the cloud services, it is highly desired to devise privacy-preserving frameworks in which neither of the involving parties is required to reveal their private information. Several research works have been developed to address privacy-preserving computing for DL networks, e.g., [GBDL<sup>+</sup>16, MZ17]. The existing solutions, however, either: (i) rely on the modification of DL layers (such as non-linear activation functions) to efficiently compute the specific cryptographic protocols. For instance, authors in [GBDL<sup>+</sup>16, MZ17] have suggested the use of polynomial-based Homomorphic encryption to make the client’s data oblivious to the server. Their approach requires changing the non-linear activation functions to some polynomial approximation (e.g., square) during training. Such modification, in turn, can

|                      | Accuracy Preserving | Independency of Third-party Server | Data & Network Embedding | Supporting Distributed Clients | Support for Large Batch Sizes | Scalability for Large DL Models | Security Primitive    |

|----------------------|---------------------|------------------------------------|--------------------------|--------------------------------|-------------------------------|---------------------------------|-----------------------|

| DeepSecure           | ✓                   | ✓                                  | ✓                        | ✓                              | ✗                             | ✓                               | GC                    |

| CryptoNets (ICML'16) | ✗                   | ✓                                  | ✗                        | ✗                              | ✓                             | ✗                               | Leveled HE            |

| SecureML (S&P'17)    | ✗                   | ✗                                  | ✗                        | ✓                              | ✗                             | ✓                               | Linearly HE, GC, SS   |

| MiniONN (CCS'17)     | ✓                   | ✓                                  | ✗                        | ✓                              | ✗                             | ✓                               | Additively HE, GC, SS |

**Figure 1.5:** High-level characteristics of existing frameworks for privacy-preserving execution of deep learning models and their corresponding cryptographic primitives.

reduce the ultimate accuracy of the model and poses a trade-off between the model accuracy and execution cost of the privacy-preserving protocol. Or (ii) fall in the two-server settings in which data owners distribute their private data among two non-colluding servers to perform a particular DL inference. The two non-colluding server assumption is not ideal as it requires the existence of a trusted third-party which is not always an option in practical scenarios.

I have proposed DeepSecure, the first provably-secure framework for scalable DL-based analysis of data collected by distributed clients [RRK18]. DeepSecure is well-suited for streaming settings where clients need to dynamically analyze their data as it is collected over time without having to queue the samples to meet a certain batch size (e.g., 2600). The secure DL computation in DeepSecure is performed using Yaos Garbled Circuit (GC) protocol. My GC-optimized solution achieves more than 58-fold higher throughput per sample compared with the Microsofts secure DL framework (called CryptoNet). In addition to the GC-optimized DL realization, I introduced a set of inter-domain pre-processing techniques with insights from the data and algorithms to significantly reduce the GC protocol overhead in the context of deep learning. Extensive evaluations of various DL applications demonstrate up to two orders-of-magnitude additional runtime improvement achieved as a result of the proposed pre-processing methodology. DeepSecure also provides support for secure delegation of GC computations to a third party for clients with severe resource constraints such as embedded IoT and wearable devices. Figure 1.5 provides a high-level comparison of existing frameworks for DL execution on encrypted data.

## 1.2 Real-Time Causal Bayesian Analysis

Probabilistic learning and graphical modeling of time-series data with causal structure is a grand challenge in various scientific fields, ranging from machine learning, neurophysiology, and climatology to economics, medical imaging, and speech processing. In a variety of time-series applications, real-time dynamic updating of random variables is particularly important to enable effective decision making before the system encounters natural changes, rendering much of the collected data irrelevant to the current decision space.

By many estimates, as much as 80 percent of time-series data is semi-structured or even unstructured. Significant theoretical strides have been made to design Bayesian graphical analytics that can be used to effectively capture the causality structure of dynamic data. These set of works, however, are designed at the algorithmic and data abstraction level with complex data flows and are oblivious to the hardware characteristics. As such, they cannot be readily employed for real-time streaming settings in which the memory storage is limited and high-dimensional time-stamped data is collected from multiple sources at a high frequency. A number of accelerated tools have been reported in the literature to facilitate Bayesian graphical analysis on CPUs, GPUs, and FPGAs. The existing tools, however, are either tailored for a specific application with a restrict conjecture about the prior distribution of data (e.g., considering a simple Gaussian distribution) and/or are designed with a predominant assumption that data samples are independently and identically drawn from a certain distribution. As such, they cannot effectively capture dynamic data correlation in causal streaming applications (e.g., complex correlated time-series data). IBM has recently released a streaming system for managing and analyzing time-series data. This tool is built on up of the IBM InfoSphere general purpose platform and does not provide customized hardware accelerated solution for high-frequency applications with memory storage limitation.

As the synopsis of my prior work suggests, the hardware resource allocation and the algorithmic solution should be co-optimized to achieve the best domain-customized performance.