Accelerating research with programmable hardware

If you have a research project that can benefit from programmable hardware, and high speed, powerful computational performance, you can request access to the Microsoft Project Catapult system at the TACC by following the instructions on the Apply tab and sending a one-page proposal to catapult@microsoft.com.

Join the Catapult Academic mailing list (opens in new tab)to keep updated

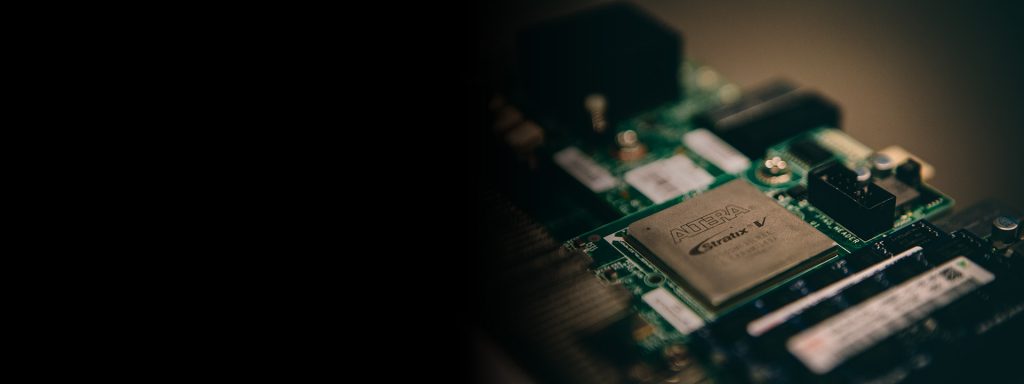

The Project Catapult Academic Program allows researchers worldwide to investigate new ways of using interconnected FPGAs as computational accelerators—a unique opportunity to access custom data center systems for high-demand research. Using the low-latency Catapult system opens up opportunities to create innovative applications and run high-demand research applications—such as machine learning and deep learning algorithms—at previously unavailable efficiencies and scale.

The Project Catapult Academic Program is run in collaboration with the Texas Advanced Computing Center (opens in new tab) (TACC) at The University of Texas at Austin, and Intel (opens in new tab). It provides researchers with free access to Microsoft Catapult FPGA systems located at TACC, including 384 Catapult nodes at TACC, and a Catapult shell development kit, tools, and examples for researchers to develop their own FPGA applications to run on the Catapult FAbRIC platform.

Researchers can request access to the Microsoft Project Catapult system at the TACC by following the instructions on the Apply tab and sending a one-page proposal to catapult@microsoft.com.

General questions regarding Project Catapult Academic Program may be sent to catapult@microsoft.com

Keep updated via the Catapult mailing list (opens in new tab)